Intel Foundry封裝與測試業務集團副總裁兼總經理Mark Gardner接受專訪,詳述該公司如何透過矽光子技術創新與共封裝光學整合策略,結合超過250個2.5D設計案例的技術積累,在AI驅動的高頻寬需求時代建立差異化競爭優勢。

面對台積電在先進封裝市場的壓倒性主導地位,Intel正透過EMIB技術的差異化創新、與Amkor等封測廠的供應鏈進行多元化合作、地理位置優勢和結構性成本優勢四個層面,建構在AI時代的競爭實力,期望能在未來晶片代工事業搶得市場先機。

設計獲採用轉營收存時間差 晶粒分級技術建立客戶信任

Intel Foundry已獲得超過250個2.5D設計案例,贏得前十大客戶中的五家。Mark坦言,設計獲採用與營收實現存在顯著時間差,因為AI加速器與高效能運算領域的設計週期特別長。

為彌補設計到量產間的信任空白,Intel採取兩項策略:在工廠運行客戶專用測試載具,支援未來幾年投產的產品;建立生產樣品,讓客戶實際體驗Intel的供應鏈合作能力。

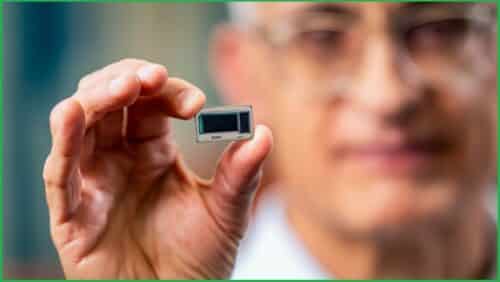

Intel的晶粒分級(die sort)技術建立在十年技術積累基礎上。Mark指出,對於擁有大型基板、多個HBM元件的AI加速器產品,在投入昂貴基板和HBM前提早發現問題晶片,價值呈指數級增長。

更關鍵的是,Intel已將客戶的晶圓級測試程式轉換到自己的晶粒分級平台,能發現其他平台直到最終測試才能發現的缺陷,為客戶提供實際驗證價值。

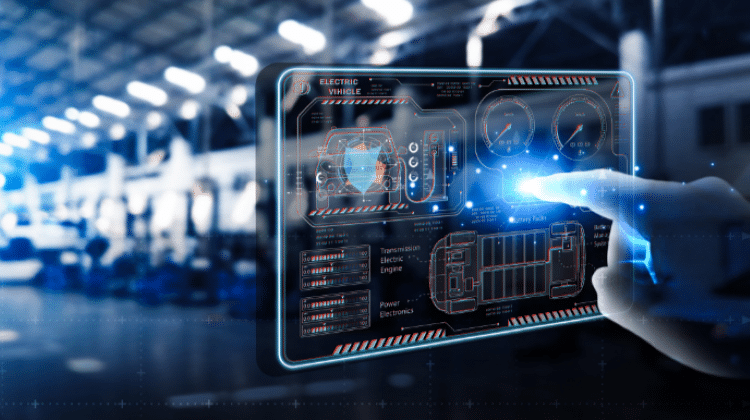

矽光子技術重新定義互連架構 i共封裝光學開創AI算力新紀元

在資料中心規模日益龐大的今天,矽光子技術的商業化進程比多數人預期的還要快。Mark指出,光的速度是電子的300倍,這個物理優勢在資料中心規模日益龐大的今天變得格外珍貴。Meta、Google這些雲端巨擘已經在測試相關方案,預計2026年將看到更大規模的部署。

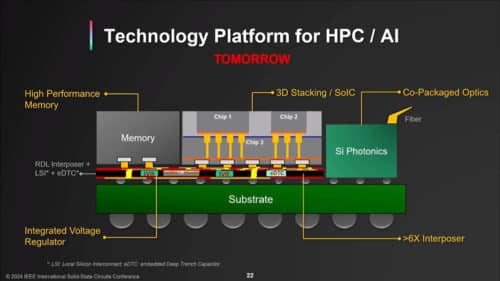

Intel在共封裝光學(CPO)領域的策略定位與眾不同。Mark表示,Intel將CPO視為與EMIB和Foveros技術互補而非競爭的技術。根據Intel的技術規劃,EMIB和Foveros技術將與CPO並行運作,例如仍可使用EMIB進行晶片對晶片、晶片對HBM連接,甚至晶片對光子堆疊連接。

由於CPO仍處於早期且分散的階段,Intel專注於與一些大型關鍵客戶合作,採用客製化的CPO與EMIB結合解決方案。這種整合策略讓Intel能夠發揮其在矽光子領域的技術積累,同時保持在封裝成本控制上的優勢。

Mark進一步解釋矽光子技術在AI運算架構中的戰略價值,他觀察到隨著模型參數量呈指數級增長,AI伺服器正呈現基建化趨勢。GPU作為算力底座,其並行計算能力是決定訓練效率的關鍵因素。傳統電互連在頻寬、延遲和功耗方面已逼近物理極限,而矽光子技術的引入將重新定義AI運算架構的性能天花板。

矽光子技術在資料中心應用的商業化價值已經開始顯現。AMD在其EPYC處理器中首度整合光學互連模組,標誌著這項技術從實驗室走向量產的關鍵轉折點。光的速度是電子的300倍,這個物理優勢在資料中心規模日益龐大的今天變得格外珍貴。

嵌入式橋接技術築競爭壁壘 供應鏈多元化突破代工迷思

Intel的EMIB技術在成本結構上具備顯著優勢。Mark解釋,EMIB採用微小矽橋接嵌入基板架構,一片晶圓可產出數千個橋接單元,晶圓利用率超過90%,遠高於傳統矽中介層技術在8倍光罩複合體製造中僅約60%的利用率。

EMIB技術還在良率和週期時間方面領先競爭對手。由於省去晶片堆疊晶圓、封膠、研磨、通矽孔暴露、凸塊製作等步驟,EMIB流程可直接進行晶片對基板組裝,徹底消除晶圓級組裝的良率損失,週期時間縮短數週。

面對封測大廠日月光和江蘇長電加強測試能力的挑戰,Intel採取持續創新策略,開發測試晶片對HBM連結的新方法、支援更大晶片佔位面積的能力,保持技術領先地位。

Intel主動建立EMIB生態系統,與Amkor等封測廠合作組裝、與多家基板供應商合作,回應客戶對多元化供應鏈的需求。在內外客戶平衡上,Mark強調Intel Foundry將所有客戶視為平等,透過產能通道機制確保外部客戶不受內部需求影響。Intel在先進封裝產能規模超過業界2倍以上,且100%的EMIB橋接和Foveros技術都在美國製造,提供地理多樣化優勢。

先進封裝技術演進 應對AI驅動大尺寸挑戰

面對當前AI晶片設計趨向更大尺寸的趨勢,Intel已經為26-27年時間框架內8至10倍光罩複合體的市場需求做好準備。Mark透露,Intel針對這種尺寸複合體的主要解決方案是EMIB或EMIB-T,目前工廠中已有相應尺寸的測試載具在運行,證明該技術將支援該時間框架內的產品。

EMIB-T代表Intel在先進封裝技術上的最新進展。這項技術加入通矽孔(TSVs),提供相對較厚的垂直銅連接,讓來自電路板下方的功率可以直接連接到上方的晶片,而不必繞過EMIB,降低較長路徑造成的功率損失。此外,EMIB-T包含銅網格作為接地平面,減少因處理器核心和其他電路突然增加工作負載而造成的功率傳輸雜訊。

Mark在專訪中透露,Intel已經有相關測試載具完成設計和新產品導入程序,並通過多輪可靠性測試。建構模組的良率和可靠性已經通過測試載具得到驗證,目前正在與客戶進行設計階段的合作。根據客戶的時程安排,預計在未來一到兩年內投入生產,具體時間取決於各客戶從設計到生產的週期。

隨著複合體尺寸增大,三大技術挑戰浮現。首先是翹曲(warpage)問題,這是大型複合體的關鍵問題之一,是Intel的關注焦點。其次是熱管理挑戰,隨著更大複合體和更高功率包絡,熱管理成為關鍵問題。Intel正與客戶合作運行熱測試載具,實施不同的熱管理技術,包括先進的熱界面材料(TIM)、微通道散熱器(IHS)等各種熱管理能力。

第三是信號完整性,隨著推動更高的輸入輸出速度、晶片對晶片資料速率,需要在嵌入基板的橋接技術、基板中的電介質材料,甚至基板的核心材料堆疊等三個向量上與基板供應商生態系統共同開發。

2030年玻璃基板導入 光電融合重定義AI架構

Mark澄清市場誤解,強調應將玻璃核心基板與9倍光罩複合體分開看待。Intel當前的有機核心基板搭配EMIB橋接路線圖已能超越9倍技術需求,玻璃基板將在2030年左右作為補強技術導入,目前正與數家關鍵供應商建立產業產能。

面對台積電和三星的玻璃基板競爭,Mark表現出信心,認為Intel透過消除整個複合體、只在基板中放置小型橋接的方式,仍具備技術和成本優勢。

Intel建構競爭優勢的策略聚焦四個層面:技術競爭力、供應鏈多樣化、地理位置優勢,以及EMIB技術的結構性成本優勢。Mark強調Intel提供靈活商業模式,客戶可選擇僅封裝服務,或與其他代工廠合作,這不是全有或全無的概念。

隨著AI模型複雜度持續增長,矽光子技術與共封裝光學將成為Intel技術路線圖重要組成。當傳統電互連逼近物理極限,矽光子的300倍速度優勢將重新定義AI運算架構,Intel正將此技術與EMIB、Foveros深度整合,創造光電融合封裝架構,為下一代AI運算奠定基礎。

面對台積電在CoWoS技術的市場主導地位,Intel正以矽光子為核心的共封裝光學解決方案,結合嵌入式多晶片互連橋接技術的成本優勢與供應鏈多元化策略,在光互連時代建立差異化競爭地位。

隨著客製化CPO解決方案的早期部署和2026年更大規模商用預期,Intel的光電融合技術布局正為下一代AI運算架構奠定基礎。同時也作為進入晶圓代工產業的重要武器。